ICPackage(IC封装形式)是指由芯片(Die),不同类型的框架(L / F)和模塑料(EMC)形成的不同形状的封装。 ICPackage的类型很多,可以根据以下标准进行分类:按包装材料划分:金属包装,陶瓷包装,塑料包装。

金属包装主要用于军事或航空技术,而没有商业产品;陶瓷包装优于金属包装,还用于军工产品,占领少量商业市场;塑料包装因其成本低,工艺简单,可靠性高而占据了大部分市场份额,因此被用于消费类电子产品。根据与PCB板的连接方式,分为:PTH封装和SMT封装PTH -PinThroughHole,通孔型; SMT-SurfaceMount技术,表面贴装型。

目前,市场上大多数集成电路都是SMT型的,根据封装外观可分为SOT,SOIC,TSSOP,QFN,QFP,BGA,CSP等。决定包装形式的两个关键因素:包装效率。

芯片面积/封装面积应尽可能接近1:1;引脚数。销的数量越多,销的数量就越多,但是加工的难度相应地增加了。

其中,由于采用了FlipChip技术和裸芯片封装技术,CSP的芯片面积/封装面积达到了1:1,是目前最先进的技术。 QFN— QuadFlatNo-leadPackage SOIC-SmallOutlineIC小尺寸IC封装TSSOP-ThinSmallShrinkOutlinePackage QFP-QuadFlatPackage四方扁平封装BGA-BallGridArrayPackage球栅阵列封装CSP-ChipScalePackage芯片级封装ICPackageStructure(IC结构图)RawMaterialinAssembly(封装) [LeadFrame]引线框提供电路连接和管芯固定;主要材料为铜,并在其上进行银,NiPdAu等材料。

L / F工艺容易腐蚀,易氧化,存放在湿度小于40%RH的氮气柜中;除BGA和CSP外,其他软件包将使用LeadFrame,而BGA将使用Substrate。 [GoldWire]焊接金线,实现芯片与外部引线框架的电气和物理连接;金线使用99.99%的高纯度金;同时,出于成本考虑,目前有铜线和铝线工艺。

优点是降低了成本,增加了工艺难度,降低了产量。线径决定了可以传导的电流; 0.8百万,1.0百万,1.3百万,1.5百万和2.0百万; MoldCompound模塑料/环氧树脂的主要成分是:环氧树脂和各种添加剂(固化剂,改性剂,脱模剂,着色剂,阻燃剂等);主要功能是:将Die和LeadFrame包裹在熔融状态,以提供物理和电气保护,以抵抗外界干扰。

储存条件:零下5度储存,需要在室温下重新加热24小时; [环氧树脂]银浆组合物是环氧树脂填充的金属粉末(Ag);具有三个功能:在DiePad上修复Die;散热,导电功能;存放在低于-50°的温度下,并在使用前重新加热24小时; FOL-FrontofLine前端工艺FOL-BackGrinding背面研磨将对晶圆进行晶圆背面研磨,以将晶圆减薄至所需的封装厚度(8密耳〜10密耳);抛光晶片时,有必要在正面(ActiveArea)上粘贴胶带,以保护电路区域并同时对背面进行抛光。研磨后,撕下胶带并测量厚度; FOL-WaferSaw晶片切割将晶片粘贴在蓝色薄膜(聚酯薄膜)上,这样即使在切割后也不会散落;整个晶圆被SawBlade Dice切成单块,便于后续的DieAttach和其他工艺; WaferWash主要清洗锯期间产生的各种灰尘,并清洗Wafer;然后清洗Wafer。

FOL-2ndOpticalInspection两灯检查主要用于在WaferSaw之后在显微镜下观察Wafer的外观以及是否有任何浪费。 FOL-DieAttach芯片附着芯片的拾取过程:1. EjectorPin将芯片从晶片下方的Mylar提起,从而易于分离蓝色薄膜; 2.收集器/拾起器从上方拾取芯片以完成从晶片到L / F的运输过程。

3.收集器使用一定的力用银浆将芯片Bond放置在L / F垫上,具体位置是可控制的; 4. BondHeadResolution:X-0.2um; Y-0.5um; Z-1.25um; 5. BondHeadSpeed:1.3m / s; FOL-EpoxyCure银浆固化银浆固化:175°C,1小时; N2环境,以防止氧化:DieAttach质量检查:DieShear(切屑剪切力)FOL-Wire使用高纯度的键合引线键合金线(Au),铜线(Cu)或铝线(Al)通过焊接连接焊盘和引线。垫是电路的外在点。

公司: 深圳市捷比信实业有限公司

电话: 0755-29796190

邮箱: tao@jepsun.com

产品经理: 陆经理

QQ: 2065372476

地址: 深圳市宝安区翻身路富源大厦1栋7楼

更多资讯

获取最新公司新闻和行业资料。

- 什么是发光二极管封装 发光二极管封装是指发光芯片的封装,与集成电路封装有很大不同。发光二极管封装不仅需要保护灯芯,还需要能够透光。因此,发光二极管封装对封装材料有特殊要求。...

- 单层芯片电容是什么 单层芯片电容器具有体积小、应用频率高、损耗低的特点,广泛应用于移动通信、雷达、航空航天等各种射频模块电路设计中,起到隔离、旁路、滤波、耦合等作用,是微波电路中必不可少的电子元件。单层芯片电容器属于无源...

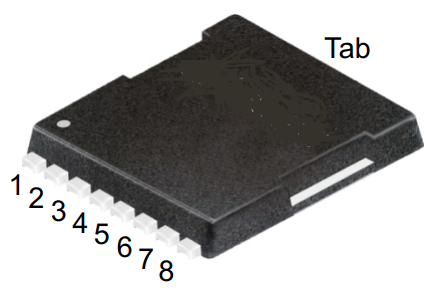

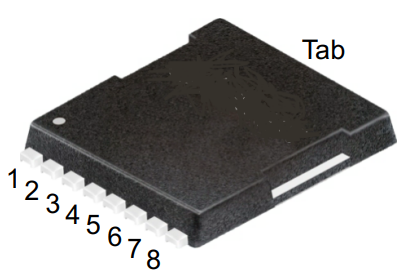

- TOLL封装是一种表面贴装型封装 TOLL封装是一种表面贴装型封装,所需空间比常见的D2PAK封装小27%。它也属于4引脚型封装,能够对栅极驱动的信号源端子进行开尔文连接,从而减小封装中源极线的电感,进而发挥MOSFET高速开关性能。TOLL封装的优点是体积小,可靠...

- TOLL封装是一种表面贴装型封装 TOLL封装是一种表面贴装型封装,所需空间比常见的D2PAK封装小27%。它也属于4引脚型封装,能够对栅极驱动的信号源端子进行开尔文连接,从而减小封装中源电阻。 TOLL封装的MOSFET由于其封装形式具有小体积、低封装电阻、低寄生...

- 铝壳电阻器的主要特点是什么?和普通电阻器有什么区别? 铝壳电阻器的主要物理特征是将电能转化为热能,可以说是电流通过时产生内部能量的耗能部件。外壳由铝合金制成(金色铝壳),表面有散热槽,体积小、功率大、耐高温,过载能力强,耐候性强,精度高,标准低感应电阻,...

- 保险丝的结构和外形是什么? 保险丝的结构和外形主要包括以下几个部分:保险丝座:保险丝座通常是一个塑料或金属制成的外壳,用于安装保险丝。保险丝芯:保险丝芯通常由两端的金属片和中间的细丝缆组成。金属片可以用来连接电路的两端,而细丝缆...

- DIOFET是什么?工作原理和应用领域详解 DIOFET,全称为Diodes Incorporated的肖特基整合式MOSFET,是一种结合了肖特基二极管与MOSFET优点的新型半导体器件。这种技术由Diodes Incorporated公司开发,旨在提供更高的效率、更快的开关速度以及更低的导通电阻,特别适用于需要高效...

- 保险丝的过温保护功能是什么? 保险丝的过温保护功能是指其能够在电路中出现过温时自动熔断,以保护电路中的其他元件不受损坏。过温是指电路或元件的温度超过其正常工作温度,可能会导致元件老化、损坏或甚至着火。保险丝的过温保护功能通常通过在...

- 保险丝的过载保护功能是什么? 保险丝的过载保护功能是指其能够在电路中的电流超过其额定电流时自动熔断,以保护电路中的其他元件不受损坏。保险丝的过载保护功能是其最基本的功能之一,可以防止电路因过载而损坏。保险丝的额定电流是指保险丝在正...

- 电感和电容之间的关系是什么? 电感和电容之间的关系是什么?电感和电容是电路中常见的两种无源元件,它们之间有着密切的关系。首先,电感器和电容器都可以储存能量。电感器储存磁场能量,而电容器储存电场能量。当电感和电容的值满足一定条件时,...

- 贴片热敏电阻是什么 贴片热敏电阻是属于敏感类的元器件,它分为正温度系数的PTC热敏电阻,和负温度系数的NTC热敏电阻,PTC热敏电阻温度越高的时候,电阻值也就越大,而NTC热敏电阻则恰恰相反。温度越高,电阻值反而就越低。贴片热敏电阻由半...

- 为什么有些压敏电阻可以用作冲击测试? 压敏电阻可以用作冲击测试,其原理是基于压敏电阻的压敏特性和冲击信号的特点。具体来说,压敏电阻可以用来检测冲击信号的幅度和持续时间。由于压敏电阻的电阻值会随着外加压力的变化而变化,因此可以通过测量压敏电...

- ESD静电抑制管的优点和缺点是什么? ESD静电抑制管具有以下优点和缺点:优点:(1)能够有效地抑制ESD损坏,保护电子设备的安全运行。 (2)能够提高电子设备的可靠性和可维护性。 (3)可以在高速电路中提供高速的电流通路,以确保电路的正常运...

- 压敏电阻的电阻值可以通过多种方式进行测量,例如什么是最常用的方法? 压敏电阻的电阻值可以通过多种方式进行测量,其中最常用的方法是使用万用表来测量。这种方法非常简单和方便,可以在家中或办公室中进行。使用万用表测量压敏电阻的电阻值的步骤如下:选择合适的万用表。数字万用表可...

- 选择贴片电感和贴片磁珠时需要考虑什么 在电路设计中,贴片电感和贴片磁珠都是常用的被动元器件。它们在电子设备中起到滤波、隔离、匹配等作用。下面将从特性、应用范围、成本等方面介绍如何在贴片电感和贴片磁珠中进行选择。 特性 (1)贴片电感:具有...

- 点火电源保险丝一装上去就爆了是什么原因 一、常见的故障现象1、发动机运转平稳性差、有爆燃、易过热的现象。2、发动机起动时有反转、怠速和急加速时有爆燃则为点火过早。3、发动机发闷无力,易过热,排气管冒黑烟,放炮则为点火过晚。二、故障原因排除及诊断...

- 贴片电阻功率指的是什么 贴片电阻的功率是指通过电流时焦耳热阻产生的功率。电阻值由贴片电阻表面上的三位数字表示,其中第一位和第二位数字是有效数字,第三位数字代表后面的零数。贴片电阻是一种体积小、重量...

- 如何正确选择精密电阻?从材料、封装到测试标准全面指南 精准选型:构建高性能电路的关键一步在现代电子系统中,尤其是涉及模拟信号处理、传感器接口和闭环控制的应用中,电阻的选择直接影响整体性能。本文将从材料、封装、额定功率、测试标准等多个维度,深入剖析如何正确...

- LW/SW系列焊接机在WLCSP芯片封装中的应用优势解析 LW/SW系列焊接机在WLCSP芯片封装中的核心价值随着半导体行业向小型化、高密度方向快速发展,WLCSP(Wafer-Level Chip Scale Package)芯片封装技术已成为主流。在此背景下,LW与SW系列焊接机凭借其卓越的精度与稳定性,成为实现高质量...

- 合金贴片电阻2512是什么功率? 合金贴片电阻2512:常规功率:1W 2W(常用) 3W特别高功率:5W 6W合金电阻参数尺寸:2512 (6432) (L6.248mm*W3.2mm)阻值:0.0003R —0.330R (0.3mR--330mR)误差:±0.5% ±1% ±5%功率:1W 1.5W 2W 3W温度系数:0.3mR ≤150PPM/°C0.5 mR -1 mR≤75PPM/°C1.1 m...